The newest technology used to construct OfA converters employs weighted capacitors instead of resistors. In this method, charged capacitors form a capacitive voltage divider wh.ise OUlpUI is proportional to the sum of the binary inputs .

Asan aid ‘in understanding the method, let us review’ the theory of cupacitivc voltage dividers. Figure 19-9 shows a two-capacitor example. The total equivalent capacitance of the two series-connected capacitors is

Therefore, the total charge delivered to the circuit, which is the same as the charge on both C1 and C~, is

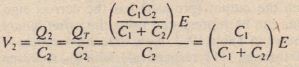

The voltage across C2 is

Similarly

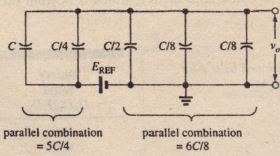

Figure 19-1O(a) shows an example of a 4-bit switched-capacitor DAC. Note that the capacitance values have binary weights. A two-phase clock is used to control switching of the capacitors. The two-phase clock consists of clock signals tPl and cP2; cPl goes high while cP2 is low, and rp2 goes high while cPl is low. When 4>1 goes high, all capacitors are switched to ground and discharged. When cPz goes high, those capacitors where the digital input is high are switched to EREF, whereas those whose inputs are low remain grounded. Figure 19-1O(b) shows the equivalent circuit when tP2 is high and the digital input is J01O. We see that the two capacitors whose digital inputs are 1 arc in parallel, as are the two capacitors whose digital inputs

(8) All capacitors are switched to ground by Those capacitors whose digital inputs arc high are switched to by

(b) Equivalent circuit when the input is 1010. The capacitors switched to are in parallel as are the ones connected to ground.

(c) Circuit equivalent to (b). The output is determined by a capacitive voltage divider

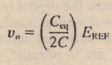

are O. The circuit is redrawn in Figure 19-10(c) wit I the parallel capacitors replacedhy their equivalents (sums). The output of the capacitive voltage divider is

The denominator in (19-9) will always be 2C, the sum or all the capacitance values in the circuit. From the foregoing analysis, we see that the output of the circuit in the general case is

where C,q is the equivalent (sum) of all the capacitors whose digital inputs are high. Table 19-2 shows the outputs for every possible input combination, and it is apparent that the analog output is proportional to the digital input. For the case where the input is 0000, note that the positive terminal of EREF in Figure 19-10 is effectively open-circuited, so the output is 0 V.

Switched-capacitor technology evolved as a means for implementing analog

functions in integrated circuits, particularly MOS circuits. It has been used to

construct filters, amplifiers, and many other special devices. The principal advantage of the technology is that small capacitors, on the order of II few picofarads. can be constructed in the integrated circuits to perform the function of the much larger capacitors that arc normally needed in low-frequency analog circuits. When capacitors are switched at a high enough frequency, they can be effectively “transformed” into other components. including resistors. The transformations arc studied from the standpoint of sampled-data theory which is beyond the scope of this book.

DAC PERFORMANCE SPECIFICATIONS

As discussed in Section 19-1, the resolution of a Df A converter is a measure of the fineness of the increments between output values. Given a fixed output voltage range, say, 0 to JO Y, a DAC that divides that range into 1024 distinct output values h. s greater resolution ,th:1O one that divides it into 512 values, Since the output

increment is directly dej cndcnt on the number of input bits, the resolution is often quoted as simply that total number of bits. The most commonly available integrated circuit converters have resolutions of R, 10.12, or 16 bits. Resolution is also expressed as the reciprocal of the total number of output voltages, often in terms of a percentage. For example, the resolution of an 8-bit DAC may be specified as

Some DAC specifications arc quoted with reference to qne or to one-half LSB (least significant bit). In this context, an LSB is simply the increment between successive output vo rages. Since an ,,-bit converter has 2/1 – I such increments,

where FSR is the full-scale range of the output voltage.

When the output of a DAC changes from one value to another, it typically overshoots the new value and may oscillate briefly around that new value before it settles to a constant voltage. The settling lime of’a DfA converter is the total time between the instant that the digital input changes and the time that the output enters a specified error band for the last. time, usually ± 112 LSn around the final value. Figure IlJ-II illustrates the specification. Settling times of typical integrated-

circuit converters range from 50 ns to several microseconds. Settling tirn : .nuy depend on the magnitude of the change at the input and is often specifie J tor a prescribed input change.

Linearity error is the maximum deviation of the analog output from the ideal output. Since the output is ideally in direct proportion to the input, the ideal output is a straight line drawn from 0 Y. Linearity error may be specified as a percentage of the full-scale range or in terms of an LSB

The Input of a DAC is said to undergo a major change when every input bit changes, as, for example, from 0 II11111 to lOO()()()OO. If the switches in Figure 19-X open faster than they close or vice versa, the output of the DAC will momentarily go to 0 or to full scale when a major change occurs, thus creating an output glitch. Glitch area is the total area of an output voltage glitch in volt-seconds or of an output current glitch in ampere-seconds. Commercial units arc often equipped with deglitchers to. minimize

An Integrated·Circuit DAC

The AD7524 CMOS integrated-circuit DAC, manufactured by Analog Devices and available from other manufacturers, is an example of an 8-bit, multiplying D/A converter. Figure \9-:2 shows a functional block diagram. Notc that the digital input is latched under the control of CS ami WR. When hoth of these control inputs

are low, the output of the DAC responds directly to the digital inputs, with no latching occurring. If either control input goes high, the digital input is latched and the analog output remains at the level corresponding to the latched data, independ I’ of any changes in the digital input. The device is then said to be in a HOLD mode, with the data bus locked out. The OUTI output is normally grounded. Maximum settling time to a ±112 LSB error band for the Texas Instruments version is 100 ns and maxin.e linearity error is ±O.2% of the full-scale range. The device can be used as a 2- or 4·quadrant multiplier and EREF can vary ±25 V